AI與機器學習賦能的晶片設計與製程協同優化(第1版)

活動訊息

內容簡介

GenAI 重塑半導體的未來

面對摩爾定律(Moore's Law)趨緩的巨大挑戰,半導體產業迫切需要新的突破點。這本書正是為了解決這個每年耗費產業數百億美元的「效率黑洞」而生。

《AI與機器學習賦能的晶片設計與製程協同優化》旨在為讀者提供一套可實踐的DTCO.ML框架,展示如何運用 Machin Learning(ML)與 Generative AI(GenAI)技術,為晶片製程注入新的加速力。掌握製程變異性並優化晶片能效,徹底擺脫耗時、昂貴的實體試產(Tape-out)試錯循環。

您將學會:透過數據驅動,將良率(Yield)提升從依賴漫長試錯轉變為可預測、可控制的快速回報(Accelerated ROI);在每一次產品迭代中,實現顯著的能效(Energy Efficiency)飛躍;以及如何為您的團隊贏得數個月的產品上市時間(TTM)競爭優勢。

無論您是渴望提升效率的晶片設計工程師、製程研發專家,或是尋求產業「再加速」策略的管理者,本書都將為您提供經過驗證的AI 賦能策略與執行藍圖。掌握DTCO 的未來,從這裡開始。

面對摩爾定律(Moore's Law)趨緩的巨大挑戰,半導體產業迫切需要新的突破點。這本書正是為了解決這個每年耗費產業數百億美元的「效率黑洞」而生。

《AI與機器學習賦能的晶片設計與製程協同優化》旨在為讀者提供一套可實踐的DTCO.ML框架,展示如何運用 Machin Learning(ML)與 Generative AI(GenAI)技術,為晶片製程注入新的加速力。掌握製程變異性並優化晶片能效,徹底擺脫耗時、昂貴的實體試產(Tape-out)試錯循環。

您將學會:透過數據驅動,將良率(Yield)提升從依賴漫長試錯轉變為可預測、可控制的快速回報(Accelerated ROI);在每一次產品迭代中,實現顯著的能效(Energy Efficiency)飛躍;以及如何為您的團隊贏得數個月的產品上市時間(TTM)競爭優勢。

無論您是渴望提升效率的晶片設計工程師、製程研發專家,或是尋求產業「再加速」策略的管理者,本書都將為您提供經過驗證的AI 賦能策略與執行藍圖。掌握DTCO 的未來,從這裡開始。

名人推薦

《AI 與機器學習賦能的晶片設計與製程協同優化》是一本聚焦於人工智慧(AI)與機器學習(ML)技術,在半導體設計與製程中應用的專業書籍。隨著半導體產業的快速發展,晶片設計的複雜性也不斷增長,傳統的設計方法已經無法滿足現代科技需求中的高效能與高效率要求。本書透過探索先進的設計與製程協同優化(Design Technology Co-Optimization, DTCO)方法,結合機器學習與生成式AI(GenAI),為未來的半導體設計提供了全新的思路與解決方案。

本書的核心內容圍繞如何將機器學習技術與半導體製程優化深度融合,從而提升晶片設計的效率和生產力。傳統的半導體設計往往依賴大量的經驗和數據分析,但隨著製程技術的不斷複雜化,這些傳統方法已經無法應對當前設計中的挑戰。作者首先介紹了DTCO 的基本概念,並詳細闡述了其在晶片設計中的應用,如何透過設計與製程的協同優化來提升晶片的能效、性能和生產力。DTCO 的核心是將設計過程和製作過程緊密結合,透過數據分析與回饋,實現精確的設計調整與製程控制。

書中對DTCO 的描述非常具體,從設計初期的準備工作,到製程數據的分析與優化,展示了如何利用先進的技術來解決現實中的挑戰。例如,在設計與製程優化的過程中,如何利用數據來預測晶片的性能、進行時序簽核(Timing Signoff),以及根據WAT(Wafer Acceptance Test)與CP(Chip Probe)數據來進行製程優化,這些都在書中進行詳細闡述。這些技術不僅限於傳統的數據分析,更進一步導入機器學習和生成式AI,從而使得設計與製程的優化過程變得更加高效。

此外,書中也深入探討了機器學習如何驅動半導體流程優化。在這一部分,作者介紹了如何透過虛擬晶圓數據進行建立模型,並利用迴歸模型進行推論。其過程能夠幫助工程師更準確地預測晶片的性能,並在製程中即時調整設計,進一步提高生產效率。在實際應用中,這種數據驅動的方法使得設計師可以在更短的時間內完成更多的優化工作,並且能夠以更高的精度預測製程的影響,進而實現對晶片性能的精細控制。

書中也探討了生成式AI 如何幫助解決傳統設計方法中的局限性,特別是在面對高維數據與複雜的製程環境時,這項技術能夠提供更佳的的設計優化方案。生成式AI 能夠從大量的數據中學習,生成對應的虛擬數據,並對這些數據進行分析,從而優化晶片設計。在這一過程中,傳統建立模型的方法可能無法應對多變的製程環境,而生成式AI 則能夠模擬更為複雜的製程變化,並實現更高效的設計優化。生成式AI 的強大之處在於它能夠生成符合實際情況的虛擬數據,並且透過迴歸分析進行預測,進一步提升設計的準確性與效率。這部分的內容對於未來晶片設計的發展方向具有重要的指導意義,尤其是在半導體技術日新月異的今天,生成式AI 無疑將成為提升設計效率的關鍵技術。

總結來說,這本書不僅是一本專業的技術指南,還是對未來半導體設計與製程優化的一次深入預測。書中詳細介紹了如何將機器學習與生成式AI技術應用於半導體領域,並且透過實際案例展示這些技術如何實現設計與製程的協同優化,提升晶片的效能與生產力。對於半導體設計工程師、EDA開發者以及學術研究者來說,這本書提供了寶貴的技術洞見,無論是在學術界還是業界,都具有重要的參考價值。

楊家驤

國立臺灣大學電機系暨電子所 教授

本書的核心內容圍繞如何將機器學習技術與半導體製程優化深度融合,從而提升晶片設計的效率和生產力。傳統的半導體設計往往依賴大量的經驗和數據分析,但隨著製程技術的不斷複雜化,這些傳統方法已經無法應對當前設計中的挑戰。作者首先介紹了DTCO 的基本概念,並詳細闡述了其在晶片設計中的應用,如何透過設計與製程的協同優化來提升晶片的能效、性能和生產力。DTCO 的核心是將設計過程和製作過程緊密結合,透過數據分析與回饋,實現精確的設計調整與製程控制。

書中對DTCO 的描述非常具體,從設計初期的準備工作,到製程數據的分析與優化,展示了如何利用先進的技術來解決現實中的挑戰。例如,在設計與製程優化的過程中,如何利用數據來預測晶片的性能、進行時序簽核(Timing Signoff),以及根據WAT(Wafer Acceptance Test)與CP(Chip Probe)數據來進行製程優化,這些都在書中進行詳細闡述。這些技術不僅限於傳統的數據分析,更進一步導入機器學習和生成式AI,從而使得設計與製程的優化過程變得更加高效。

此外,書中也深入探討了機器學習如何驅動半導體流程優化。在這一部分,作者介紹了如何透過虛擬晶圓數據進行建立模型,並利用迴歸模型進行推論。其過程能夠幫助工程師更準確地預測晶片的性能,並在製程中即時調整設計,進一步提高生產效率。在實際應用中,這種數據驅動的方法使得設計師可以在更短的時間內完成更多的優化工作,並且能夠以更高的精度預測製程的影響,進而實現對晶片性能的精細控制。

書中也探討了生成式AI 如何幫助解決傳統設計方法中的局限性,特別是在面對高維數據與複雜的製程環境時,這項技術能夠提供更佳的的設計優化方案。生成式AI 能夠從大量的數據中學習,生成對應的虛擬數據,並對這些數據進行分析,從而優化晶片設計。在這一過程中,傳統建立模型的方法可能無法應對多變的製程環境,而生成式AI 則能夠模擬更為複雜的製程變化,並實現更高效的設計優化。生成式AI 的強大之處在於它能夠生成符合實際情況的虛擬數據,並且透過迴歸分析進行預測,進一步提升設計的準確性與效率。這部分的內容對於未來晶片設計的發展方向具有重要的指導意義,尤其是在半導體技術日新月異的今天,生成式AI 無疑將成為提升設計效率的關鍵技術。

總結來說,這本書不僅是一本專業的技術指南,還是對未來半導體設計與製程優化的一次深入預測。書中詳細介紹了如何將機器學習與生成式AI技術應用於半導體領域,並且透過實際案例展示這些技術如何實現設計與製程的協同優化,提升晶片的效能與生產力。對於半導體設計工程師、EDA開發者以及學術研究者來說,這本書提供了寶貴的技術洞見,無論是在學術界還是業界,都具有重要的參考價值。

楊家驤

國立臺灣大學電機系暨電子所 教授

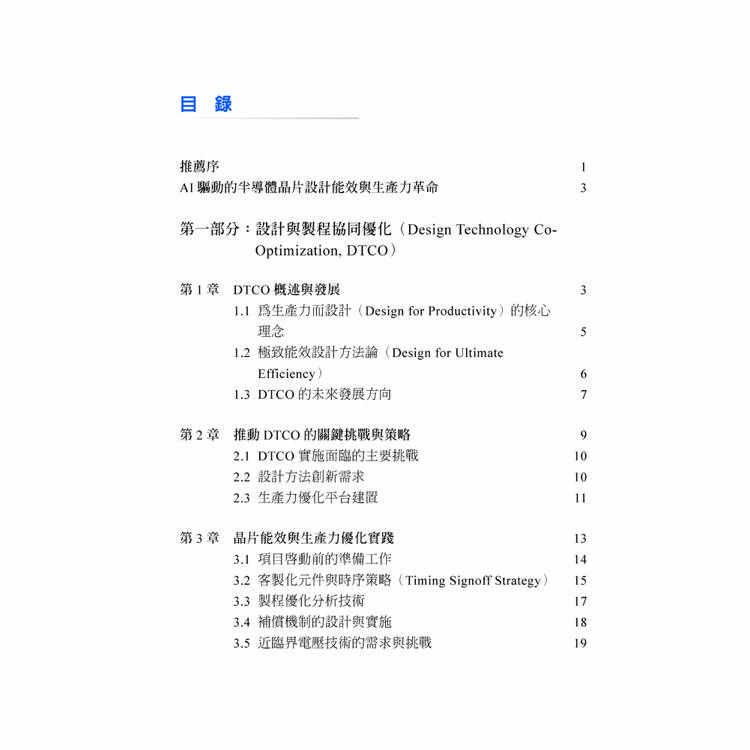

目錄

推薦序

AI 驅動的半導體晶片設計能效與生產力革命

第一部分: 設計與製程協同優化(Design Technology Co-Optimization, DTCO)

第1 章 DTCO 概述與發展

1.1 為生產力而設計(Design for Productivity)的核心理念

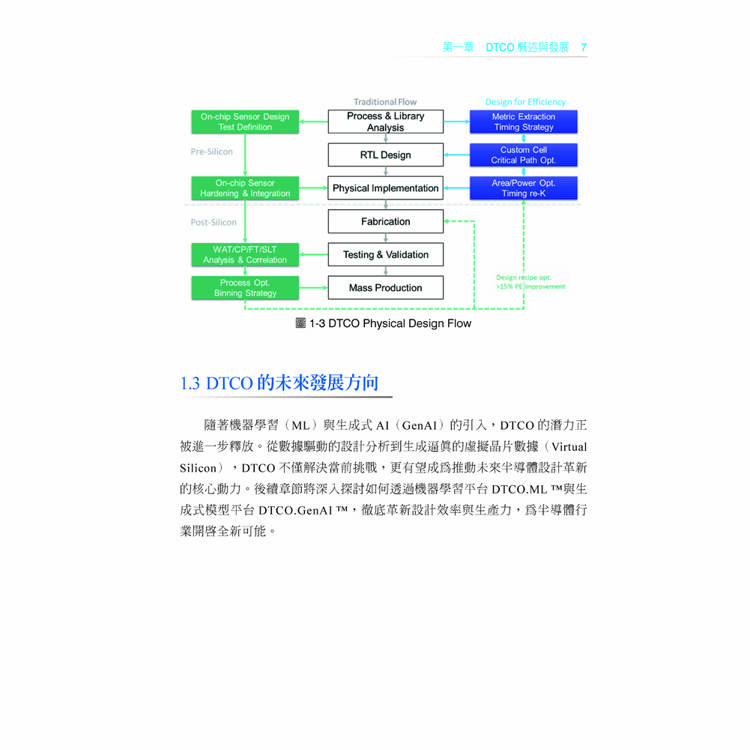

1.2 極致能效設計方法論(Design for Ultimate Efficiency)

1.3 DTCO 的未來發展方向

第2 章 推動DTCO 的關鍵挑戰與策略

2.1 DTCO 實施面臨的主要挑戰

2.2 設計方法創新需求

2.3 生產力優化平台建置

第3 章 晶片能效與生產力優化實踐

3.1 項目啟動前的準備工作

3.2 客製化元件與時序策略(Timing Signoff Strategy)

3.3 製程優化分析技術

3.4 補償機制的設計與實施

3.5 近臨界電壓技術的需求與挑戰

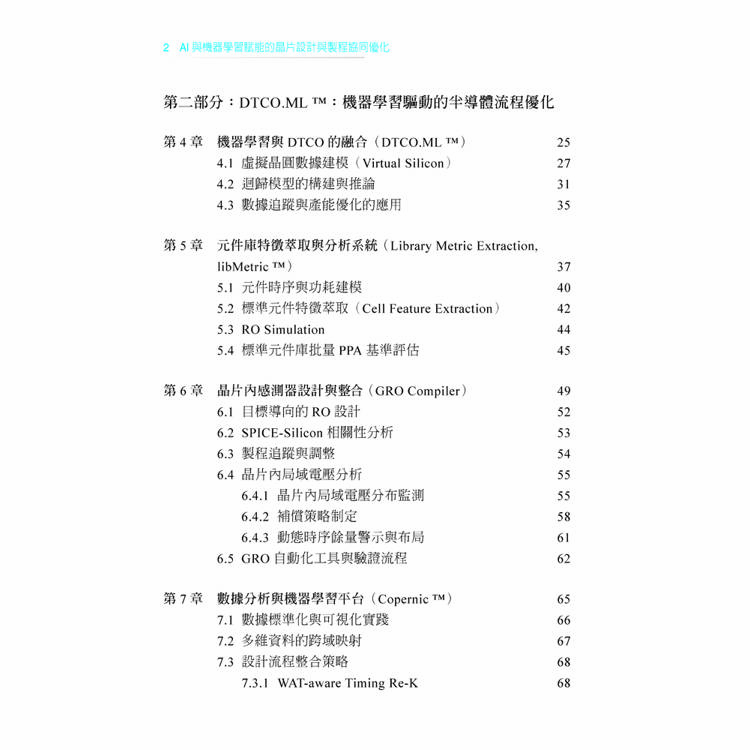

第二部分:DTCO.ML ™:機器學習驅動的半導體流程優化

第4 章 機器學習與DTCO 的融合(DTCO.ML ™)

4.1 虛擬晶圓數據建模(Virtual Silicon)

4.2 迴歸模型的構建與推論

4.3 數據追蹤與產能優化的應用

第5 章 元件庫特徵萃取與分析系統(Library Metric Extraction, libMetric ™)

5.1 元件時序與功耗建模

5.2 標準元件特徵萃取(Cell Feature Extraction)

5.3 RO Simulation

5.4 標準元件庫批量PPA 基準評估

第6 章 晶片內感測器設計與整合(GRO Compiler)

6.1 目標導向的RO 設計

6.2 SPICE-Silicon 相關性分析

6.3 製程追蹤與調整

6.4 晶片內局域電壓分析

6.4.1 晶片內局域電壓分布監測

6.4.2 補償策略制定

6.4.3 動態時序餘量警示與布局

6.5 GRO 自動化工具與驗證流程

第7 章 數據分析與機器學習平台(Copernic ™)

7.1 數據標準化與可視化實踐

7.2 多維資料的跨域映射

7.3 設計流程整合策略

7.3.1 WAT-aware Timing Re-K

7.3.2 WAT-CP 映射與相關性分析

7.3.3 OCV Analysis

7.4 晶片內變異性(OCV)分析與設計餘量優化

7.5 後矽製程分析與優化(Post-Silicon Analysis and Optimization)

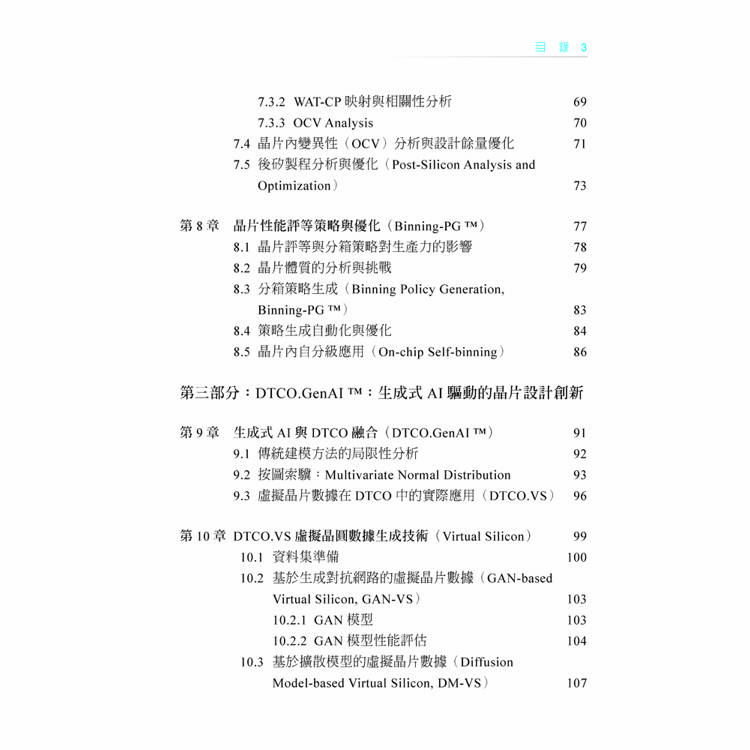

第8 章 晶片性能評等策略與優化(Binning-PG ™)

8.1 晶片評等與分箱策略對生產力的影響

8.2 晶片體質的分析與挑戰

8.3 分箱策略生成(Binning Policy Generation, Binning-PG ™)

8.4 策略生成自動化與優化

8.5 晶片內自分級應用(On-chip Self-binning)

第三部分:DTCO.GenAI ™:生成式AI 驅動的晶片設計創新

第9 章 生成式AI 與DTCO 融合(DTCO.GenAI ™)

9.1 傳統建模方法的局限性分析

9.2 按圖索驥:Multivariate Normal Distribution

9.3 虛擬晶片數據在DTCO 中的實際應用(DTCO.VS)

第10 章 DTCO.VS 虛擬晶圓數據生成技術(Virtual Silicon)

10.1 資料集準備

10.2 基於生成對抗網路的虛擬晶片數據(GAN-based Virtual Silicon, GAN-VS)

10.2.1 GAN 模型

10.2.2 GAN 模型性能評估

10.3 基於擴散模型的虛擬晶片數據(Diffusion Model-based Virtual Silicon, DM-VS)

10.3.1 去噪擴散概率模型(Denoising Diffusion Probabilitic Model)

10.3.2 Diffusion 模型性能評估

第11 章 Generative AI 驅動的晶片能效優化與建模

11.1 WAT 超分辨率(WAT Super Resolution, WATSR)

11.2 高效矽製程偏移建模(High-Efficiency SPICESilicon Bias Modeling, He-SSBM)

11.2.1 One-shot SPICE-Silicon N/P Correlation的設計原理

11.2.2 設計與防守策略優化

11.3 高效蒙地卡羅仿真近似(High-Fidelity Generative Monte Approximation, HΣ-GMA)

11.3.1 傳統Monte Carlo 方法的限制

11.3.2 生成式神經網路的創新應用

第12 章 結論與展望

12.1 機器學習與AI 賦能DTCO:革新晶片設計與製程優化(DTCO.ML ™)

12.2 生成式AI 驅動優化的未來趨勢(DTCO. GenAI ™)

12.3 創新EDA 開發與未來展望

附 錄

開源資源表列

參考文獻表列

專業術語表

AI 驅動的半導體晶片設計能效與生產力革命

第一部分: 設計與製程協同優化(Design Technology Co-Optimization, DTCO)

第1 章 DTCO 概述與發展

1.1 為生產力而設計(Design for Productivity)的核心理念

1.2 極致能效設計方法論(Design for Ultimate Efficiency)

1.3 DTCO 的未來發展方向

第2 章 推動DTCO 的關鍵挑戰與策略

2.1 DTCO 實施面臨的主要挑戰

2.2 設計方法創新需求

2.3 生產力優化平台建置

第3 章 晶片能效與生產力優化實踐

3.1 項目啟動前的準備工作

3.2 客製化元件與時序策略(Timing Signoff Strategy)

3.3 製程優化分析技術

3.4 補償機制的設計與實施

3.5 近臨界電壓技術的需求與挑戰

第二部分:DTCO.ML ™:機器學習驅動的半導體流程優化

第4 章 機器學習與DTCO 的融合(DTCO.ML ™)

4.1 虛擬晶圓數據建模(Virtual Silicon)

4.2 迴歸模型的構建與推論

4.3 數據追蹤與產能優化的應用

第5 章 元件庫特徵萃取與分析系統(Library Metric Extraction, libMetric ™)

5.1 元件時序與功耗建模

5.2 標準元件特徵萃取(Cell Feature Extraction)

5.3 RO Simulation

5.4 標準元件庫批量PPA 基準評估

第6 章 晶片內感測器設計與整合(GRO Compiler)

6.1 目標導向的RO 設計

6.2 SPICE-Silicon 相關性分析

6.3 製程追蹤與調整

6.4 晶片內局域電壓分析

6.4.1 晶片內局域電壓分布監測

6.4.2 補償策略制定

6.4.3 動態時序餘量警示與布局

6.5 GRO 自動化工具與驗證流程

第7 章 數據分析與機器學習平台(Copernic ™)

7.1 數據標準化與可視化實踐

7.2 多維資料的跨域映射

7.3 設計流程整合策略

7.3.1 WAT-aware Timing Re-K

7.3.2 WAT-CP 映射與相關性分析

7.3.3 OCV Analysis

7.4 晶片內變異性(OCV)分析與設計餘量優化

7.5 後矽製程分析與優化(Post-Silicon Analysis and Optimization)

第8 章 晶片性能評等策略與優化(Binning-PG ™)

8.1 晶片評等與分箱策略對生產力的影響

8.2 晶片體質的分析與挑戰

8.3 分箱策略生成(Binning Policy Generation, Binning-PG ™)

8.4 策略生成自動化與優化

8.5 晶片內自分級應用(On-chip Self-binning)

第三部分:DTCO.GenAI ™:生成式AI 驅動的晶片設計創新

第9 章 生成式AI 與DTCO 融合(DTCO.GenAI ™)

9.1 傳統建模方法的局限性分析

9.2 按圖索驥:Multivariate Normal Distribution

9.3 虛擬晶片數據在DTCO 中的實際應用(DTCO.VS)

第10 章 DTCO.VS 虛擬晶圓數據生成技術(Virtual Silicon)

10.1 資料集準備

10.2 基於生成對抗網路的虛擬晶片數據(GAN-based Virtual Silicon, GAN-VS)

10.2.1 GAN 模型

10.2.2 GAN 模型性能評估

10.3 基於擴散模型的虛擬晶片數據(Diffusion Model-based Virtual Silicon, DM-VS)

10.3.1 去噪擴散概率模型(Denoising Diffusion Probabilitic Model)

10.3.2 Diffusion 模型性能評估

第11 章 Generative AI 驅動的晶片能效優化與建模

11.1 WAT 超分辨率(WAT Super Resolution, WATSR)

11.2 高效矽製程偏移建模(High-Efficiency SPICESilicon Bias Modeling, He-SSBM)

11.2.1 One-shot SPICE-Silicon N/P Correlation的設計原理

11.2.2 設計與防守策略優化

11.3 高效蒙地卡羅仿真近似(High-Fidelity Generative Monte Approximation, HΣ-GMA)

11.3.1 傳統Monte Carlo 方法的限制

11.3.2 生成式神經網路的創新應用

第12 章 結論與展望

12.1 機器學習與AI 賦能DTCO:革新晶片設計與製程優化(DTCO.ML ™)

12.2 生成式AI 驅動優化的未來趨勢(DTCO. GenAI ™)

12.3 創新EDA 開發與未來展望

附 錄

開源資源表列

參考文獻表列

專業術語表

序/導讀

AI 驅動的半導體晶片設計能效與生產力革命

‧前言

在AI 生成時代,半導體產業正從傳統的良率提升,邁向以創新思維推動整體生產力優化。為在市場競爭中脫穎而出,晶片設計的焦點已不再局限於良率和成本效益,而是全面提升性能、產能與市場競爭力。本書將深入探討如何利用AI技術,全面優化設計餘量、時序簽核、測試策略、數據分析、製程配方調整、分箱策略(Binning Strategy)及系統層級補償方案,從而推動半導體設計與生產力的革新。

‧書籍定位

本書以晶片實體設計流程的視角切入,聚焦於機器學習技術(ML)在半導體產業與製程協同優化(DTCO)領域的應用。內容涵蓋從傳統機器學習到最前沿的生成式AI 技術(GenAI),全面探討如何有效提升晶片設計效能與生產力。

‧目標讀者

半導體產業人士:為晶片設計工程師、EDA 開發者及學術研究者,提供實例參考與技術洞見。

相關及跨領域的研究者:幫助加深對DTCO 技術的理解,並探索 AI 技術的應用潛力。

‧書籍架構

本書將介紹DTCO 的基本概念與原理,深入探討機器學習在設計與製程優化中的應用,並分析生成式 AI 如何塑造半導體設計的創新與未來發展。此外,我們將探討創新性 EDA 發展的潛力,探索新技術如何加速設計流程並提升效能。

‧前言

在AI 生成時代,半導體產業正從傳統的良率提升,邁向以創新思維推動整體生產力優化。為在市場競爭中脫穎而出,晶片設計的焦點已不再局限於良率和成本效益,而是全面提升性能、產能與市場競爭力。本書將深入探討如何利用AI技術,全面優化設計餘量、時序簽核、測試策略、數據分析、製程配方調整、分箱策略(Binning Strategy)及系統層級補償方案,從而推動半導體設計與生產力的革新。

‧書籍定位

本書以晶片實體設計流程的視角切入,聚焦於機器學習技術(ML)在半導體產業與製程協同優化(DTCO)領域的應用。內容涵蓋從傳統機器學習到最前沿的生成式AI 技術(GenAI),全面探討如何有效提升晶片設計效能與生產力。

‧目標讀者

半導體產業人士:為晶片設計工程師、EDA 開發者及學術研究者,提供實例參考與技術洞見。

相關及跨領域的研究者:幫助加深對DTCO 技術的理解,並探索 AI 技術的應用潛力。

‧書籍架構

本書將介紹DTCO 的基本概念與原理,深入探討機器學習在設計與製程優化中的應用,並分析生成式 AI 如何塑造半導體設計的創新與未來發展。此外,我們將探討創新性 EDA 發展的潛力,探索新技術如何加速設計流程並提升效能。

配送方式

-

台灣

- 國內宅配:本島、離島

-

到店取貨:

不限金額免運費

-

海外

- 國際快遞:全球

-

港澳店取:

訂購/退換貨須知

退換貨須知:

**提醒您,鑑賞期不等於試用期,退回商品須為全新狀態**

-

依據「消費者保護法」第19條及行政院消費者保護處公告之「通訊交易解除權合理例外情事適用準則」,以下商品購買後,除商品本身有瑕疵外,將不提供7天的猶豫期:

- 易於腐敗、保存期限較短或解約時即將逾期。(如:生鮮食品)

- 依消費者要求所為之客製化給付。(客製化商品)

- 報紙、期刊或雜誌。(含MOOK、外文雜誌)

- 經消費者拆封之影音商品或電腦軟體。

- 非以有形媒介提供之數位內容或一經提供即為完成之線上服務,經消費者事先同意始提供。(如:電子書、電子雜誌、下載版軟體、虛擬商品…等)

- 已拆封之個人衛生用品。(如:內衣褲、刮鬍刀、除毛刀…等)

- 若非上列種類商品,均享有到貨7天的猶豫期(含例假日)。

- 辦理退換貨時,商品(組合商品恕無法接受單獨退貨)必須是您收到商品時的原始狀態(包含商品本體、配件、贈品、保證書、所有附隨資料文件及原廠內外包裝…等),請勿直接使用原廠包裝寄送,或於原廠包裝上黏貼紙張或書寫文字。

- 退回商品若無法回復原狀,將請您負擔回復原狀所需費用,嚴重時將影響您的退貨權益。

商品評價